10. I/O Port

10.1 Introduction to GPIO

CH559 provides up to 45 I / O pins, some pins have alternate functions. Among them, the input and output of ports P0 ~ P3 and the output of P4 can be bit-addressed.

If the pin is not configured as an alternate function, the default is the general-purpose I/O pin state. When used as a general-purpose digital I/O, all I/O ports have a true “read-modify-write” function, which supports bit manipulation instructions such as SETB or CLR to independently change the direction of certain pins or port levels.

10.2 GPIO Register

All registers and bits in this section are expressed in a common format: the lowercase “n” represents the serial number of the port (n = 0, 1, 2, 3), and the lowercase “x” represents the serial number of the bit (x = 0, 1, 2, 3, 4, 5, 6, 7).

Table 10.2.1 GPIO Register List

| Name | Address | Description | Reset value |

|---|---|---|---|

| P0 | 80h | P0 port input and output register | FFh |

| P0_DIR | C4h | P0 port direction control register | 00h |

| P0_PU | C5h | Port 0 pull-up enable register | 00h/FFh |

| P1 | 90h | P1 port input and output register | FFh |

| P1_IE | B9h | P1 port input enable register | FFh |

| P1_DIR | BAh | P1 port direction control register | 00h |

| P1_PU | BBh | P1 port pull-up enable register | FFh |

| P2 | A0h | P2 port input and output register | FFh |

| P2_DIR | BCh | P2 port direction control register | 00h |

| P2_PU | BDh | P2 port pull-up enable register | FFh |

| P3 | B0h | P3 port input and output register | FFh |

| P3_DIR | BEh | P3 port direction control register | 00h |

| P3_PU | BFh | P3 port pull-up enable register | FFh |

| P4_OUT | C0h | P4 port output register | 00h |

| P4_IN | C1h | P4 port input register (read only) | FFh |

| P4_DIR | C2h | P4 port direction control register | 00h |

| P4_PU | C3h | P4 port pull-up enable register | FFh |

| P4_CFG | C7h | P4 port configuration register | 00h |

| P5_IN | C7h | P5 port input register (read only) | 00h |

| PIN_FUNC | CEh | Pin Function Select Register | 00h |

| PORT_CFG | C6h | Port Configuration Register | 0Fh |

| XBUS_SPEED | FDh | Bus speed configuration register | FFh |

| XBUS_AUX | A2h | Bus auxiliary setting register | 00h |

Port configuration register (PORT_CFG):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:4] | bPn_DRV | RW | Pn port output drive capability selection, this bit is 0 to select the drive current 5mA level. This bit is 1 for P0 / P2 / P3 to select the drive current 20mA level, and for P1 to select the drive current 10mA level | 0000b |

| [3:0] | bPn_OC | RW | Pn port open-drain output enable, this bit is 0 to set the port as push-pull output. This bit is 1 to set the port to be open-drain output | 1111b |

Pn port input and output register (Pn):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | Pn.0~Pn.7 | RW | Pn.x pin status input and data output bits, bit-addressable | FFh |

Pn port direction control register (Pn_DIR):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | Pn_DIR | RW | Pn.x pin direction setting | 00h |

P0 port pull-up enable register (P0_PU) and Pn port pull-up enable register (Pn_PU), where n = 1/2/3:

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | P0_PU | RW | P0.x pin pull-up resistor is enabled (when En_P0_Pullup = 0 is configured) | 00h | P0.x pin pull-up resistor is enabled (when En_P0_Pullup = 1 is configured) | FFh |

| [7:0] | Pn_PU | RW | Pn.x pin pull-up resistor is enabled, this bit is 0 to disable pull-up; this bit is 1 to enable pull-up | FFh |

The configuration of the Pn port is implemented by the combination of the bit bPn_OC in the PORT_CFG, the port direction control register Pn_DIR, and the port pull-up enable register Pn_PU, as follows.

Table 10.2.2 Port configuration register combinations

| bPn_OC | Pn_DIR | Pn_PU | Description |

|---|---|---|---|

| 0 | 0 | 0 | High-impedance input mode, no pull-up resistor on pin |

| 0 | 0 | 1 | Pull-up input mode, pins have pull-up resistors |

| 0 | 1 | x | Push-pull output mode, with symmetrical driving ability, can output or absorb large current |

| 1 | 0 | 0 | High-impedance input weak quasi-bidirectional mode, open-drain output, no pull-up resistor on pin |

| 1 | 1 | 0 | High-impedance input quasi-bidirectional mode, open-drain output, no pull-up resistor on the pin, when the output changes from low to high, it automatically drives high for 2 clock cycles to speed up the conversion |

| 1 | 0 | 1 | Weak quasi-bidirectional mode (imitation of 8051), open-drain output, support input, pin with pull-up resistor |

| 1 | 1 | 1 | Quasi-bidirectional mode (standard 8051), open-drain output, support input, pins have pull-up resistors, when the output changes from low to high, it automatically drives high for 2 clock cycles to speed up the conversion |

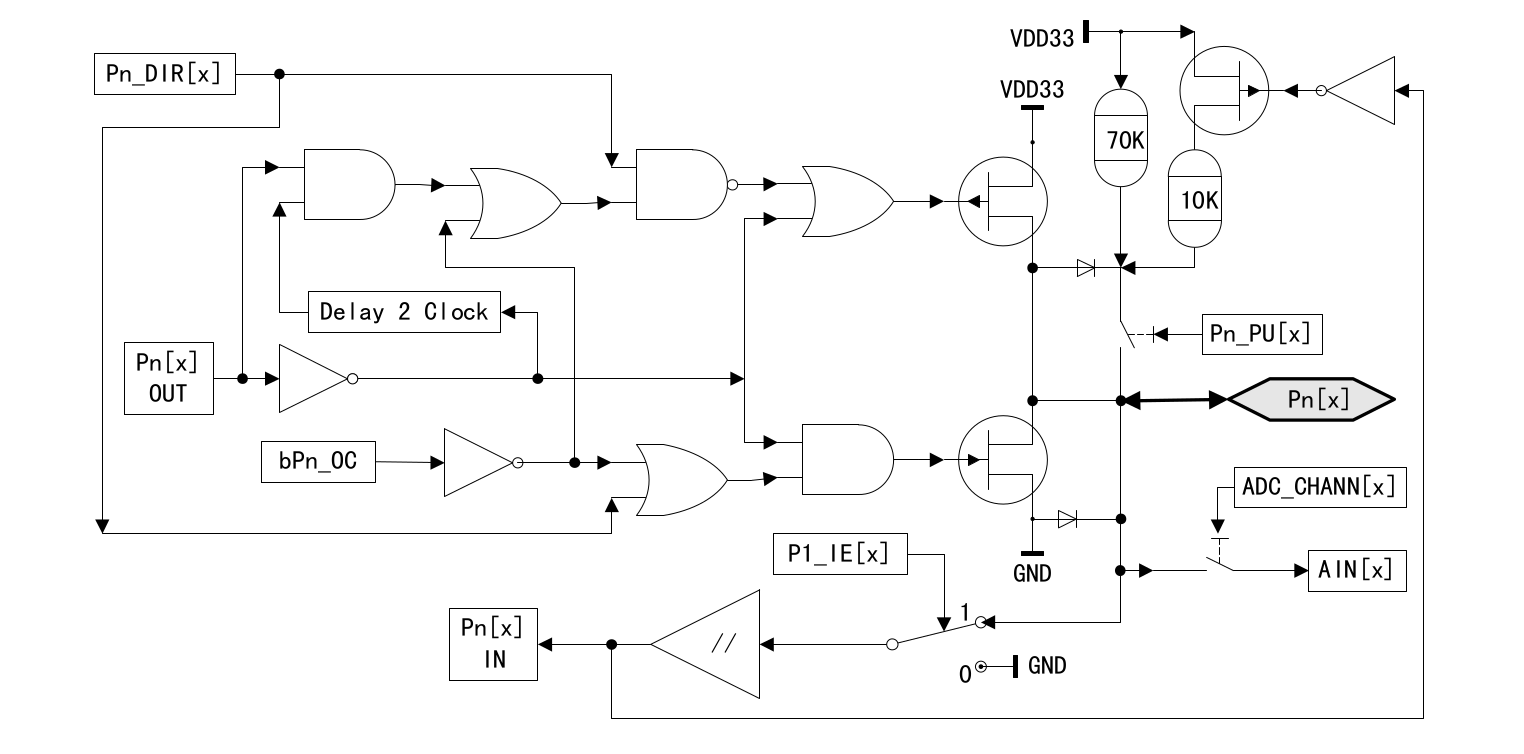

Ports P0~P3 support pure input or push-pull output and quasi-bidirectional modes. Port P4 supports pure input or push-pull output and other modes. Each pin has a freely controllable internal pull-up resistor connected to VDD33, and a protection diode connected to GND.

Figure 10.2.1 is the equivalent schematic of the P1.x pin of the P1 port. After removing P1_IE and AIN and ADC_CHANN, it can be applied to the P0, P2, and P3 ports.

Figure 10.2.1 I/O pin equivalent schematic

P1 port input enable register (P1_IE):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | P1_IE | RW | P1.x pin input enable, if this bit is 0, the pin is used for ADC analog input, digital input is disabled. If this bit is 1, the digital input is enabled | FFh |

10.3 P4 port

P4 port output register (P4_OUT):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | P4_OUT.0~P4_OUT.7 | RW | P4.x pin data output bit, bit-addressable | 00h |

P4 port input register (P4_IN):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | P4_IN | R0 | P4.x pin status input bit | FFh |

P4 port pull-up enable register (P4_PU):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | P4_PU | RW | P4.x pin pull-up resistor is enabled, this bit is 0 to disable pull-up; this bit is 1 to enable pull-up | FFh |

P4 port direction control register (P4_DIR):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | P4_DIR | RW | P4.x pin direction setting, this bit is 0 for input; this bit is 1 for output | 00h |

P4 port configuration register (P4_CFG) and P5 port input register (P5_IN):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | P5.7 | R0 | P5.7 pin status input bit | 0 |

| 6 | bIO_INT_ACT | R0 | GPIO interrupt request activation status: When bIE_IO_EDGE = 0, this bit is 1 to indicate the GPIO input active level, interrupt will be requested, and 0 to indicate the input invalid level. When bIE_IO_EDGE = 1, this bit is used as an edge interrupt flag. A value of 1 indicates that a valid edge was detected.This bit cannot be cleared by software. It can only be automatically cleared during reset or level interrupt mode or when entering the corresponding interrupt service routine zero | 0 |

| 5 | P5.5 | R0 | P5.5 pin status input bit with built-in controllable pull-down resistor | 0 |

| 4 | P5.4 | R0 | P5.4 pin status input bit with built-in controllable pull-down resistor | 0 |

| 3 | bSPI0_PIN_X | RW | SPI0 pin SCS / SCK mapping enable. If this bit is 0, P1.4 / P1.7 is used. If this bit is 1, P4.6 / P4.7 is used | 0 |

| 2 | bP4_DRV | RW | P4 port output drive capability selection, this bit is 0 to select the drive current 5mA level. This bit is 1 to select the drive current 20mA level | 0 |

| 1 | P5.1 | R0 | P5.1 pin status input bit with built-in controllable pull-down resistor | 0 |

| 0 | P5.0 | R0 | P5.0 pin status input bit with built-in controllable pull-down resistor | 0 |

10.4 GPIO Multiplexing and Mapping

Some of the I / O pins of CH559 have alternate functions. After power-on, they are all general-purpose I / O pins. After different function modules are enabled, the corresponding pins are configured as the corresponding function pins of the respective function modules.

Pin function selection register (PIN_FUNC):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bPWM1_PIN_X | RW | PWM1/PWM2 pin mapping enable bit, if this bit is 0, PWM1/2 uses P2.4/P2.5. If this bit is 1, PWM1/2 uses P4.3/P4.5 | 0 |

| 6 | bTMR3_PIN_X | RW | PWM3/CAP3 pin mapping enable bit. When this bit is 0, PWM3/CAP3 uses P1.2. When this bit is 1, PWM3/CAP3 uses P4.2 | 0 |

| 5 | bT2EX_PIN_X | RW | T2EX/CAP2 pin mapping enable bit. When this bit is 0, T2EX/CAP2 uses P1.1. When this bit is 1, T2EX/CAP2 uses P2.5 | 0 |

| 4 | bUART0_PIN_X | RW | UART0 pin mapping enable bit. When this bit is 0, RXD0/TXD0 uses P3.0/P3.1. When this bit is 1, RXD0/TXD0 uses P0.2/P0.3. | 0 |

| 3 | bXBUS_EN | RW | xBUS external bus function enable bit, this bit is 0 to disable the external bus; this bit is 1 to enable the P0 port as an 8-bit data bus, and P3.6/P3.7 as write/read strobe control during bus access | 0 |

| 2 | bXBUS_CS_OE | RW | xBUS external bus chip select output enable bit. This bit is 0 to disable the output of chip select and can be decoded by external circuits. P3.4 is set as CS0 when this bit is 1 (XCS0 chip select 0, active low), and When ALE is disabled, the bus address A15 is inverted and output to P3.3 (equivalent to chip select 1, active low) | 0 |

| 1 | bXBUS_AH_OE | RW | xBUS External bus high 8-bit address output enable bit, this bit is 0 to disable output. When this bit is 1, during the MOVX_@DPTR instruction access to the external bus, the P2 port output bus address is the upper 8 bits | 0 |

| 0 | bXBUS_AL_OE | RW | The lower 8-bit address output enable bit of the xBUS external bus. When this bit is 0, it is a multiplexed address mode. When accessing the external bus, the lower 8 bits of the address are multiplexed with the data bus as required, and the external circuit is controlled by ALE to latch. If this bit is 1, it is the direct address mode.The lower 8-bit addresses A0~A7 are output through P4.0~P4.5 and P3.5 and P2.7. | 0 |

Figure 10.2.1 I/O pin equivalent schematic

| GPIO | Other functions: in order of priority from left to right |

|---|---|

| P0[0] | AD0, UDTR/bUDTR, P0.0 |

| P0[1] | AD1, URTS/bURTS, P0.1 |

| P0[2] | AD2, RXD_/bRXD_, P0.2 |

| P0[3] | AD3, TXD_/bTXD_, P0.3 |

| P0[4] | AD4, UCTS/bUCTS, P0.4 |

| P0[5] | AD5, UDSR/bUDSR, P0.5 |

| P0[6] | AD6, URI/bURI, P0.6 |

| P0[7] | AD7, UDCD/bUDCD, P0.7 |

| P1[0] | AIN0, T2/bT2, CAP1/bCAP1, P1.0 |

| P1[1] | AIN1, T2EX/bT2EX, CAP2/bCAP2, P1.1 |

| P1[2] | AIN2, PWM3/bPWM3, CAP3/bCAP3, P1.2 |

| P1[3] | AIN3, P1.3 |

| P1[4] | AIN4, SCS/bSCS, P1.4 |

| P1[5] | AIN5, MOSI/bMOSI, P1.5 |

| P1[6] | AIN6, MISO/bMISO, P1.6 |

| P1[7] | AIN7, SCK/bSCK, P1.7 |

| P2[0] | A8, P2.0 |

| P2[1] | MOSI1/bMOSI1, A9, P2.1 |

| P2[2] | MISO1/bMISO1, A10, P2.2 |

| P2[3] | SCK1/bSCK1, A11, P2.3 |

| P2[4] | PWM1/bPWM1, A12, P2.4 |

| P2[5] | TNOW/bTNOW, PWM2/bPWM2, A13, T2EX_/bT2EX_, CAP2_/bCAP2_, P2.5 |

| P2[6] | RXD1/bRXD1, A14, P2.6 |

| P2[7] | TXD1/bTXD1, DA7/bDA7, A15, P2.7 |

| P3[0] | RXD/bRXD, P3.0 |

| P3[1] | TXD/bTXD, P3.1 |

| P3[2] | LED0/bLED0, INT0/bINT0, P3.2 |

| P3[3] | LED1/bLED1, !A15, INT1/bINT1, P3.3 |

| P3[4] | LEDC/bLEDC, XCS0/bXCS0, T0/bT0, P3.4 |

| P3[5] | DA6/bDA6, T1/bT1, P3.5 |

| P3[6] | WR/bWR, P3.6 |

| P3[7] | RD/bRD, P3.7 |

| P4[0] | LED2/bLED2, A0, RXD1_/bRXD1_, P4.0 |

| P4[1] | A1, P4.1 |

| P4[2] | PWM3_/bPWM3_, CAP3_/bCAP3_, A2, P4.2 |

| P4[3] | PWM1_/bPWM1_, A3, P4.3 |

| P4[4] | LED3/bLED3, TNOW_/bTNOW_, TXD1_/bTXD1_, A4, P4.4 |

| P4[5] | PWM2_/bPWM2_, A5, P4.5 |

| P4[6] | XI, SCS_/bSCS_, P4.6 |

| P4[7] | XO, SCK_/bSCK_, P4.7 |

| P5[0] | DM/bDM, P5.0 |

| P5[1] | DP/bDP, P5.1 |

| P5[4] | HM/bHM, ALE, XB, P5.4 |

| P5[5] | HP/bHP, !A15, XA, P5.5 |

| P5[7] | RST/bRST, P5.7 |

The priority order from left to right described in the above table refers to the priority order when multiple functional modules compete to use the GPIO. For example, the P2 port has been set to the upper 8 bits of the output bus address. If only the A8~A11 addresses are actually used, then P2.4/P2.5 can still be used for higher priority PWM1/PWM2 functions, P2.6 It can still be used for RXD1 function, P2.7 can still be used for higher priority TXD1 or DA7 functions, so as to avoid wasting P2.4~P2.7 pins when A12~A15 address is not used.