12. Timer

12.1 Timer 0/1

Timer0 / 1 are two 16-bit timer / counters. TCON and TMOD are used to configure Timer0 and Timer1. TCON is used for timer / counter T0 and T1 start control and overflow interrupt and external interrupt control. Each timer is a 16-bit timing unit consisting of two 8-bit registers. The high byte counter of timer 0 is TH0, the low byte is TL0; the high byte counter of timer 1 is TH1, and the low byte is TL1. Timer 1 can also be used as a baud rate generator for UART0.

Table 12.1.1 List of Timer 0/1 related registers

| Name | Address | Description | Reset value |

|---|---|---|---|

| TH1 | 8Dh | Timer1 count high byte | xxh |

| TH0 | 8Ch | Timer0 count high byte | xxh |

| TL1 | 8Bh | Timer1 count low byte | xxh |

| TL0 | 8Ah | Timer0 count low byte | xxh |

| TMOD | 89h | Timer0 / 1 mode register | 00h |

| TCON | 88h | Timer0 / 1 control register | 00h |

Timer/Counter 0/1 Control Register (TCON):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | TF1 | RW | Timer1 overflow interrupt flag bit, it is automatically cleared after entering Timer 1 interrupt | 0 |

| 6 | TR1 | RW | Timer1 start / stop bit, set to 1 to start, set or cleared by software | 0 |

| 5 | TF0 | RW | Timer0 overflow interrupt flag bit, enters timer 0 and is automatically cleared after interrupt | 0 |

| 4 | TR0 | RW | Timer0 start / stop bit, set to 1 to start, set or cleared by software | 0 |

| 3 | IE1 | RW | INT1 Interrupt request flag bit for external interrupt 1; it is automatically cleared after entering interrupt | 0 |

| 2 | IT1 | RW | INT1 External interrupt 1 trigger mode control bit. This bit is 0 to select the external interrupt to trigger at low level. This bit is 1 to select the external interrupt to trigger at falling edge. | 0 |

| 1 | IE0 | RW | INT0 Interrupt request flag for external interrupt 0. It is automatically cleared after entering interrupt | 0 |

| 0 | IT0 | RW | INT0 External interrupt 0 trigger mode control bit. This bit is 0 to select the external interrupt to trigger at low level. This bit is 1 to select the external interrupt to trigger at falling edge. | 0 |

Timer/Counter 0/1 Mode Register (TMOD):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bT1_GATE | RW | The gate enable bit controls whether Timer1 start is affected by external interrupt signal INT1. If this bit is 0, whether Timer/Counter 1 is started has nothing to do with INT1. If this bit is 1, it can be started only when INT1 pin is high and TR1 is 1 | 0 |

| 6 | bT1_CT | RW | Timing or counting mode selection bit, this bit is 0 to work in timing mode. This bit is 1 to work in counting mode, using the falling edge of T1 pin as clock | 0 |

| 5 | bT1_M1 | RW | Timer/Counter 1 mode selection high | 0 |

| 4 | bT1_M0 | RW | Timer/Counter 1 mode selection low | 0 |

| 3 | bT0_GATE | RW | Gating enable bit, controls whether Timer0 start is affected by external interrupt signal INT0. If this bit is 0, the timer/counter 0 is started regardless of INT0. If this bit is 1, only the INT0 pin is high and TR0 can be started | 0 |

| 2 | bT0_CT | RW | Timing or counting mode selection bit, this bit is 0 to work in timing mode; this bit is 1 to work in counting mode, using the falling edge of T0 pin as clock | 0 |

| 1 | bT0_M1 | RW | Timer/Counter 0 Mode selection high | 0 |

| 0 | bT0_M0 | RW | Timer/Counter 0 Mode selection low | 0 |

Table 12.1.2 bTn_M1 and bTn_M0 select Timern operating mode (n = 0, 1)

| bTn_M1 | bTn_M0 | Timern working mode (n = 0, 1) |

|---|---|---|

| 0 | 0 | Mode 0: 13-bit timer / counter n. The counting unit consists of the lower 5 bits of TLn and THn. The upper 3 bits of TLn are invalid. When the count changes from all 13 bits to all 0s, the overflow flag TFn is set and the initial value needs to be reset |

| 0 | 1 | Mode 1: 16-bit timer / counter n. The counting unit consists of TLn and THn. When the count changes from all 16 bits to all 0s, the overflow flag TFn is set and the initial value needs to be reset |

| 1 | 0 | mode 2: 8-bit reload timer / counter n, the counting unit uses TLn, THn as the reload counting unit. When the count changes from all 8 bits to all 0s, the overflow flag TFn is set and the initial value is automatically loaded from THn |

| 1 | 1 | Mode 3: If it is timer / counter 0, then timer / counter 0 is divided into two parts TL0 and TH0, TL0 is used as an 8-bit timer / counter and occupies all control bits of Timer0; and TH0 also serves as another 8-bit timer Use, occupy TR1, TF1 and interrupt resources of Timer1, and Timer1 is still available at this time, but the start control bit TR1 and overflow flag bit TF1 cannot be used. In the case of Timer / Counter 1, entering Mode 3 will stop Timer / Counter 1. |

Timern count low byte (TLn) (n = 0, 1):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | TLn | RW | Timern count low byte | xxh |

Timern count high byte (THn) (n = 0, 1):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | TLn | RW | Timern count high byte | xxh |

12.2 Timer2

Timer2 is a 16-bit auto-reload timer/counter. It is configured through the T2CON and T2MOD registers. The high byte counter of timer 2 is TH2 and the low byte is TL2. Timer2 can be used as the baud rate generator of UART0. It also has two signal level capture functions. The capture count is stored in RCAP2 and T2CAP1 registers.

Table 12.2.1 List of Timer2 related registers

| Name | Address | Description | Reset value |

|---|---|---|---|

| TH2 | CDh | Timer2 Counter High Byte | 00h |

| TL2 | CCh | Timer2 counter low byte | 00h |

| T2COUNT | CCh | TL2 and TH2 form 16-bit SFR | 0000h |

| T2CAP1H | CDh | Timer2 Capture 1 data high byte (read only) | xxh |

| T2CAP1L | CCh | Timer2 capture 1 data low byte (read only) | xxh |

| T2CAP1 | CCh | T2CAP1L and T2CAP1H form a 16-bit SFR | xxxxh |

| RCAP2H | CBh | Count Reload/Capture 2 Data Register High Byte | 00h |

| RCAP2L | CAh | Count Reload/Capture 2 Data Register Low Byte | 00h |

| RCAP2 | CAh | RCAP2L and RCAP2H form a 16-bit SFR | 0000h |

| T2MOD | C9h | Timer2 mode register | 00h |

| T2CON | C8h | Timer2 Control Register | 00h |

Timer/Counter 2 Control Register (T2CON):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | TF2 | RW | When bT2_CAP1_EN = 0, it is the overflow interrupt flag of Timer2. When Timer2 counts from 16 bits are all 1 to all 0, setting the overflow flag to 1 requires software to clear it; when RCLK = 1 or TCLK When = 1, this bit will not be set to 1 | 0 |

| 7 | CAP1F | RW | When bT2_CAP1_EN = 1, it is Timer2 capture 1 interrupt flag, which is triggered by the valid edge of T2 and needs to be cleared by software | 0 |

| 6 | EXF2 | RW | Timer2 external trigger flag. When EXEN2 = 1, it is set by T2EX valid edge trigger. Need to be cleared by software. | 0 |

| 5 | RCLK | RW | UART0 receive clock selection, this bit is 0 to select the baud rate generated by Timer1 overflow pulse; this bit is 1 to select the baud rate generated by Timer2 overflow pulse | 0 |

| 4 | TCLK | RW | UART0 transmit clock selection, this bit is 0 to select the baud rate generated by Timer1 overflow pulse; this bit is 1 to select the baud rate generated by Timer2 overflow pulse | 0 |

| 3 | EXEN2 | RW | T2EX trigger enable bit, this bit is 0 to ignore T2EX. This bit is 1 to enable triggering reload or capture on T2EX valid edge | 0 |

| 2 | TR2 | RW | Timer2 start / stop bit, set to 1 to start, set or cleared by software | 0 |

| 1 | C_T2 | RW | Timer2 clock source selection bit, this bit is 0 to use the internal clock; this bit is 1 to use the edge count based on the falling edge of the T2 pin | 0 |

| 0 | CP_RL2 | RW | Timer2 function selection bit. If RCLK or TCLK is 1, this bit should be forced to 0. If this bit is 0, Timer2 is used as a timer / counter, and it can automatically reload the initial count value when the counter overflows or the T2EX level changes; this bit is 1 to enable the capture 2 function of Timer2 and capture the valid edge of T2EX | 0 |

Timer/Counter 2 Mode Register (T2MOD):

| Bit | Name | Access | Description | Reset value | |

|---|---|---|---|---|---|

| 7 | bTMR_CLK | RW | The fast clock mode enable of the T0 / T1 / T2 timer of the fast clock has been selected. If this bit is 1, the system clock Fsys without frequency division is used as the count clock. If this bit is 0, the frequency division clock is used. This bit has no effect on the timer that selects the standard clock | 0 | |

| 6 | bT2_CLK | RW | Timer2 internal clock frequency selection bit. This bit is 0 to select the standard clock. The timing / counting mode is Fsys / 12. UART0 clock mode is Fsys / 4. This bit is 1 to select the fast clock. = 0) or Fsys (bTMR_CLK = 1), the UART0 clock mode is Fsys / 2 (bTMR_CLK = 0) or Fsys (bTMR_CLK = 1) | 0 | |

| 5 | bT1_CLK | RW | Timer1 internal clock frequency selection bit. This bit is 0 to select the standard clock Fsys / 12. For 1 to select the fast clock Fsys / 4 (bTMR_CLK = 0) or Fsys (bTMR_CLK = 1) | 0 | |

| 4 | bT0_CLK | RW | Timer0 internal clock frequency selection bit. This bit is 0 for the standard clock Fsys / 12. For 1 it is the fast clock Fsys / 4 (bTMR_CLK = 0) or Fsys (bTMR_CLK = 1) | 0 | |

| 3 | bT2_CAP_M1 | RW | Timer2 capture mode high | Capture mode selection: X0: from falling edge to falling edge 01: From any edge to any edge, that is, the level changes 11: from rising edge to rising edge | 0 |

| 2 | bT2_CAP_M0 | RW | Timer2 capture mode low | 0 | |

| 1 | T2OE | RW | Timer2 clock output enable bit, this bit is 0 to disable the output. This bit is 1 to enable the T2 pin output clock, the frequency is half of the Timer2 overflow rate | 0 | |

| 0 | bT2_CAP1_EN | RW | Capture 1 mode is enabled when RCLK = 0, TCLK = 0, CP_RL2 = 1, C_T2 = 0, T2OE = 0, this bit is 1 to enable capture 1 function to capture the valid edge of T2. This bit is 0 to disable capture 1 | 0 | |

Count Reload / Capture 2 Data Register (RCAP2):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | RCAP2H | RW | High byte of reload value in timer / counter mode. High byte of timer captured by CAP2 in capture mode | 00h |

| [7:0] | RCAP2L | RW | Low byte of reload value in timer / counter mode. Low byte of timer captured by CAP2 in capture mode | 00h |

Timer2 counter (T2COUNT), only valid when bT2_CAP1_EN = 0:

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | TH2 | RW | High byte of current counter | 00h |

| [7:0] | TL2 | RW | Low byte of current counter | 00h |

Timer2 capture 1 data (T2CAP1), only valid when bT2_CAP1_EN = 1:

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T2CAP1H | RW | High byte of timer captured by CAP1 | xxh |

| [7:0] | T2CAP1L | RW | Low byte of timer captured by CAP1 | xxh |

12.3 Timer3

Table 12.3.1 List of Timer3 related registers

| Name | Address | Description | Reset value |

|---|---|---|---|

| T3_FIFO_H | AFh | FIFO high byte of Timer3 | xxh |

| T3_FIFO_L | AEh | FIFO low byte of Timer3 | xxh |

| T3_FIFO | AEh | T3_FIFO_L and T3_FIFO_H form a 16-bit SFR | xxxxh |

| T3_DMA_AH | ADh | DMA current buffer address high byte | 0xh |

| T3_DMA_AL | ACh | DMA current buffer address low byte | xxh |

| T3_DMA | ACh | T3_DMA_AL and T3_DMA_AH form a 16-bit SFR | 0xxxh |

| T3_DMA_CN | ABh | DMA Remaining Count Register | 00h |

| T3_CTRL | AAh | Timer3 Control Register | 02h |

| T3_STAT | A9h | Timer3 status register | 00h |

| T3_END_H | A7h | Timer3 count end high byte | xxh |

| T3_END_L | A6h | Timer3 low end byte count | xxh |

| T3_END | A6h | T3_END_L and T3_END_H form a 16-bit SFR | xxxxh |

| T3_COUNT_H | A5h | Timer3 current count high byte (read only) | 00h |

| T3_COUNT_L | A4h | Timer3 current count low byte (read only) | 00h |

| T3_COUNT | A4h | T3_COUNT_L and T3_COUNT_H form a 16-bit SFR | 0000h |

| T3_CK_SE_H | A5h | Timer3 clock division setting high byte | 00h |

| T3_CK_SE_L | A4h | Timer3 clock division setting low byte | 20h |

| T3_CK_SE | A4h | T3_CK_SE_L and T3_CK_SE_H form a 16-bit SFR | 0020h |

| T3_SETUP | A3h | Timer3 setting register | 04h |

Timer3 setup register (T3_SETUP):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bT3_IE_END | RW | This bit is 1 to enable the capture mode count timeout interrupt or the PWM mode cycle end interrupt. This bit is 0 to disable the enable | 0 |

| 6 | bT3_IE_FIFO_OV | RW | This bit is 1 to enable the FIFO overflow interrupt. This bit is 0 to disable the enable | 0 |

| 5 | bT3_IE_FIFO_REQ | RW | This bit is 1 to enable capture mode FIFO> = 4 interrupt or PWM mode FIFO <= 3 interrupt; this bit is 0 to disable enable | 0 |

| 4 | bT3_IE_ACT | RW | This bit is 1 to enable the capture mode input signal to activate the interrupt or PWM mode data to trigger the interrupt; this bit is 1 to disable the enable | 0 |

| 3 | reserve | R0 | reserve | 0 |

| 2 | bT3_CAP_IN | R0 | Input level of the current capture pin after noise filtering | 1 |

| 1 | bT3_CAP_CLK | RW | This bit is 1 to enable input capture without minimum pulse width limitation.It is only valid when T3_CK_SE is 1.It is used to capture high speed signals. | 0 |

| 0 | bT3_EN_CK_SE | RW | This bit is 1 to enable access to the clock divider setting register; this bit is 0 to enable access to the current count register | 0 |

Timer3 current count (T3_COUNT), only valid when bT3_EN_CK_SE = 0:

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T3_COUNT_H | RO | Timer3 current count high byte | 00h |

| [7:0] | T3_COUNT_L | RO | Timer3 current count low byte | 00h |

Timer3 clock division setting register (T3_CK_SE), only valid when bT3_EN_CK_SE = 1:

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T3_CK_SE_H | RW | Timer3 clock divider high byte, only the lower 4 bits are valid, the upper 4 bits are fixed to 0 | 00h |

| [7:0] | T3_CK_SE_L | RW | Low byte of Timer3 clock divider | 20h |

Timer3 count end value register (T3_END):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T3_END_H | RW | Timer3 count end high byte | xxh |

| [7:0] | T3_END_L | RW | Timer3 count end low byte | xxh |

Timer3 status register (T3_STAT):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bT3_IF_DMA_END | RW | DMA Complete Interrupt Flag. A 1 in this bit indicates an interrupt. A 0 in this bit indicates no interrupt. Cleared on write 1 or cleared on T3_DMA_CN | 0 |

| 6 | bT3_IF_FIFO_OV | RW | A 1 in this bit indicates a FIFO overflow interrupt. A 0 in this bit indicates no interrupt. Write 1 clear | 0 |

| 5 | bT3_IF_FIFO_REQ | RW | When this bit is 1, it indicates that the FIFO data interrupt flag is requested. In capture mode, it is triggered by FIFO> = 4, and in PWM mode, it is triggered by FIFO <= 3. If this bit is 0, there is no interrupt. Write 1 clear | 0 |

| 4 | bT3_IF_ACT | RW | When bT3_IE_ACT = 1, this bit is 1 to indicate that the capture mode input signal activates the interrupt or the PWM mode data triggers the interrupt. This bit is 0 without interrupt. Cleared on write 1 or cleared when accessing FIFO | 0 |

| 4 | bT3_IF_END | RW | When bT3_IE_ACT = 0, this bit is 1 to indicate the capture mode count timeout interrupt or PWM mode cycle end interrupt. If this bit is 0, there is no interrupt. Write 1 clear | 0 |

| [3:0] | MASK_T3_FIFO_CNT | R0 | Timer3's current FIFO count | 0000b |

Timer3 control register (T3_CTRL):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bT3_CAP_M1 | RW | Timer3 capture edge mode high. PWM data repeat mode high | 0 |

| 6 | bT3_CAP_M0 | RW | Timer3 capture edge mode low bit. PWM data repeat mode high bit | 0 |

| 5 | bT3_PWM_POLAR | RW | PWM output polarity control bit in PWM mode. If this bit is 0, the default low level is valid, and the high level is valid.If this bit is 1, the default high level is active, and the low level is valid. | 0 |

| 5 | bT3_CAP_WIDTH | RW | In capture mode, the minimum capture pulse width setting bit. If this bit is 0, at least 4 frequency division clock cycles are valid. | 0 |

| 4 | bT3_DMA_EN | RW | This bit is 1 to enable Timer3's DMA and DMA interrupts. 0 to disable it | 0 |

| 3 | bT3_OUT_EN | RW | This bit is 1 to enable the PWM output of Timer3. This bit is 0 to disable | 0 |

| 2 | bT3_CNT_EN | RW | This bit is 1 to enable Timer3 counting. This bit is 0 to pause counting | 0 |

| 1 | bT3_CLR_ALL | RW | This bit is 1 to clear the Timer3 count and FIFO, which needs to be cleared by software | 1 |

| 0 | bT3_MOD_CAP | RW | Timer3 mode selection bit. If this bit is 0, Timer3 works in timer/count or PWM mode.If this bit is 1, it works in capture mode. | 0 |

In capture mode, bT3_CAP_M1 and bT3_CAP_M0 select the capture edge: when bT3_CAP_M1 and bT3_CAP_M0 are 00, the capture mode is turned off or suspended; when it is 01, the edge is activated by any edge, that is, the change in level, and the capture is from any edge to any edge; when it is 10 Activated by falling edge, capture from falling edge to falling edge. When it is 11, activate by rising edge, capture from rising edge to rising edge.

In PWM mode, bT3_CAP_M1 and bT3_CAP_M0 select the number of data repetitions: When bT3_CAP_M1 and bT3_CAP_M0 are 00, the data is not reused, that is, a new data is used every PWM cycle. When it is 01, the data is reused 4 times, that is, the same data is used for continuous 4 PWM cycles. When it is 10, the data is reused 8 times. When it is 11, the data is reused 16 times.

DMA remaining count register (T3_DMA_CN):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T3_DMA_CN | RW | The current remaining DMA count, which can be preset to the initial value, and is automatically reduced after the DMA operation | 00h |

DMA current buffer address (T3_DMA):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T3_DMA_AH | RW | The current high byte of the DMA address, which can be preset to the initial value. It automatically increases after DMA. Only the lower 4 bits are valid. The upper 4 bits are fixed to 0. Only the first 4K of xRAM are supported. | 0xh |

| [7:0] | T3_DMA_AL | RW | Low byte of the current DMA address, which can be preset to the initial value. It is automatically increased after DMA. Only the upper 7 bits are valid. The lowest bit is fixed at 0. Only even addresses are supported. | xxh |

FIFO port (T3_FIFO):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | T3_FIFO_H | RW | FIFO high byte of Timer3 | xxh |

| [7:0] | T3_FIFO_L | RW | FIFO low byte of Timer3 | xxh |

12.4 PWM Function

Timer3 of CH559 has a 16-bit PWM function. In addition, there are two other 8-bit PWMs. The PWM can choose the default output polarity to be low or high. It can dynamically modify the PWM output duty cycle. After the simple RC resistor and capacitor perform integral low-pass filtering, various output voltages can be obtained, which is equivalent to a low-speed digital-to-analog converter DAC.

PWM3 output duty cycle = T3_FIFO / T3_END, the support range is 0% to 100%. If the value of T3_FIFO is greater than T3_END, it is treated as 100%.

PWM1 output duty cycle = PWM_DATA / PWM_CYCLE, support range 0% to 100%, if the value of PWM_DATA is greater than PWM_CYCLE, it will be treated as 100%.

PWM2 output duty cycle = PWM_DATA2 / PWM_CYCLE, the support range is 0% to 100%. If the value of PWM_DATA2 is greater than PWM_CYCLE, it is treated as 100%.

In practical applications, it is recommended to allow the PWM pin output and set the PWM output pin to push-pull output mode.

12.4.1 PWM1 and PWM2

Table 12.4.1 List of PWM1 and PWM2 related registers

| Name | Address | Description | Reset value |

|---|---|---|---|

| PWM_CYCLE | 9Fh | 3 | xxh |

| PWM_CK_SE | 9Eh | 3 | 00h |

| PWM_CTRL | 9Dh | 3 | 02h |

| PWM_DATA | 9Ch | 3 | xxh |

| PWM_DATA2 | 9Bh | 3 | xxh |

PWM2 data register (PWM_DATA2):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | PWM_DATA2 | RW | Store current data of PWM2, duty cycle of PWM2 output active level = PWM_DATA2 / PWM_CYCLE | xxh |

PWM1 data register (PWM_DATA):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | PWM_DATA | RW | Store the current data of PWM1, the duty cycle of PWM1 output active level = PWM_DATA / PWM_CYCLE | xxh |

PWM control register (PWM_CTRL):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bPWM_IE_END | RW | This bit is 1 to enable the end of the PWM cycle or the MFM buffer empty interrupt | 0 |

| 6 | bPWM2_POLAR | RW | When bPWM_MOD_MFM = 0, control the output polarity of PWM2. When this bit is 0, the default low level is valid, and the high level is valid. When the bit is 1, it is default high level and the low level is active | 0 |

| 6 | bMFM_BUF_EMPTY | R0 | When bPWM_MOD_MFM = 1, this bit is 1 to indicate that the MFM buffer is empty | 0 |

| 5 | bPWM_POLAR | RW | Controls the polarity of PWM1 output. If this bit is 0, it defaults to low level, and the high level is valid. If this bit is 1, it defaults to high level, and the low level is valid. | 0 |

| 4 | bPWM_IF_END | RW | PWM cycle end interrupt flag bit, this bit is 1 means there is an interrupt, cleared by writing 1 or cleared by writing PWM_CYCLE or cleared when reloading data | 0 |

| 3 | bPWM_OUT_EN | RW | PWM1 output enable, this bit is 1 to enable PWM1 output | 0 |

| 2 | bPWM2_OUT_EN | RW | When bPWM_MOD_MFM = 0, this bit is 1 to enable PWM2 output | 0 |

| 2 | bMFM_BIT_CNT2 | R0 | When bPWM_MOD_MFM = 1, it indicates the current MFM encoding progress. This bit is 0 to indicate that the lower 4 bits are being processed. A 1 indicates that the upper 4 bits are being processed. | 0 |

| 1 | bPWM_CLR_ALL | RW | This bit is 1 to clear the PWM1 and PWM2 counts and FIFOs and needs to be cleared by software | 1 |

| 0 | bPWM_MOD_MFM | RW | MFM encoding mode is enabled, this bit is 0 for PWM mode. This bit is 1 for MFM mode | 0 |

PWM clock division setting register (PWM_CK_SE):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | PWM_CK_SE | RW | Setting the PWM Clock Divisor | 00h |

PWM cycle period register (PWM_CYCLE):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | PWM_CYCLE | RW | Set the PWM cycle period, when the value is 00h, it means 100h | xxh |

12.5 Timer Function

12.5.1 Timer0/1

- Set T2MOD to select the internal clock frequency of the timer. If bTn_CLK (n = 0/1) is 0, then the clock corresponding to Timer0/1 is Fsys/12; if bTn_CLK is 1, then select Fsys by bTMR_CLK = 0 or 1. / 4 or Fsys as the clock.

- Set the TMOD to configure the working mode of the timer.

- Set the timer/counter initial values TLn and THn (n = 0/1).

- Set the bit TRn (n = 0/1) in TCON to start or stop the timer/counter. It can be queried by bit TFn (n = 0/1) or detected by interrupt mode.

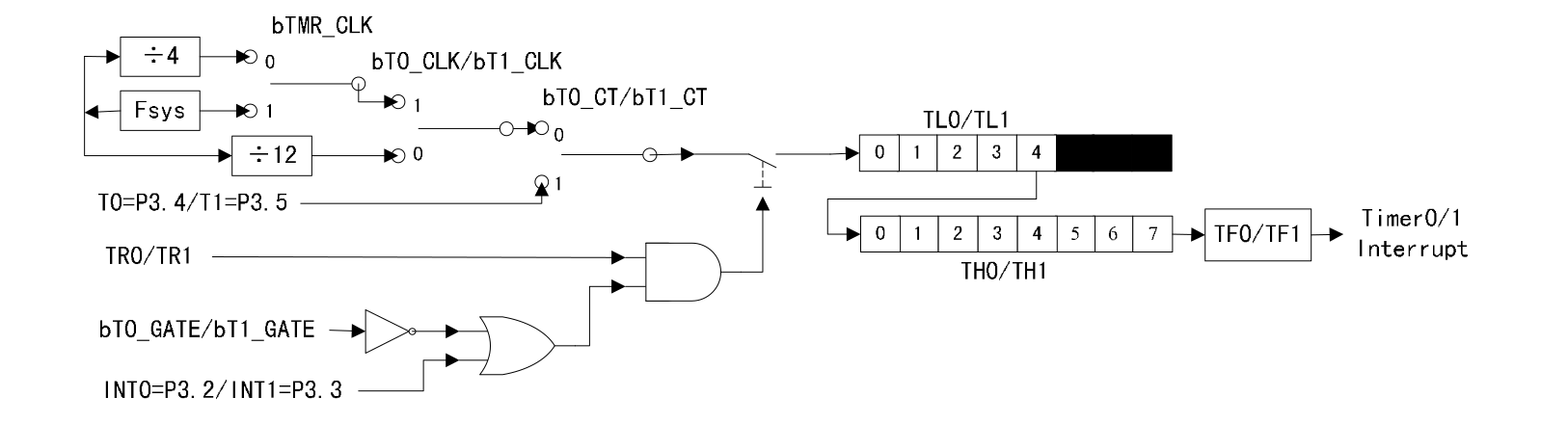

Mode 0: 13-bit timer/counter

Figure 12.5.1.1 Timer0/1 Mode 0

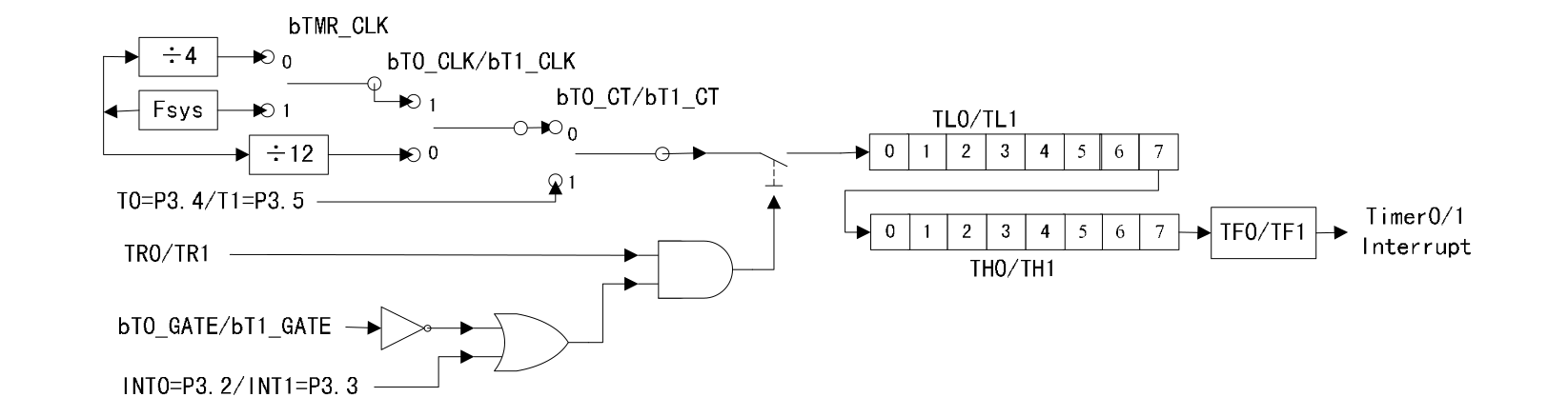

Mode 1: 16-bit timer/counter

Figure 12.5.1.2 Timer0/1 Mode 1

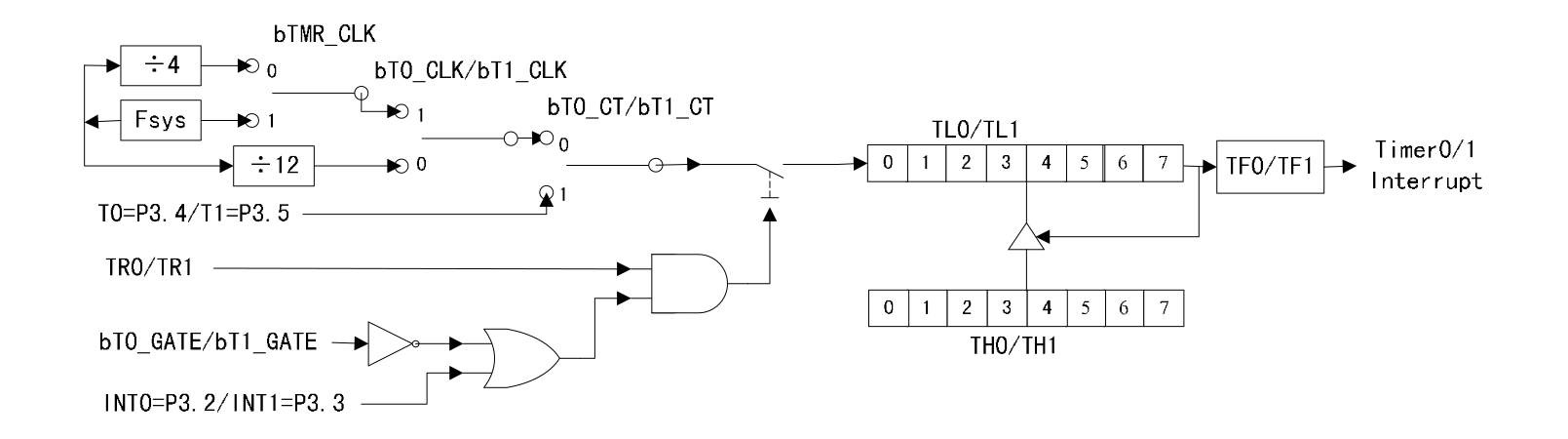

Mode 2: Automatic reload 8-bit timer/counter

Figure 12.5.1.3 Timer0/1 Mode 2

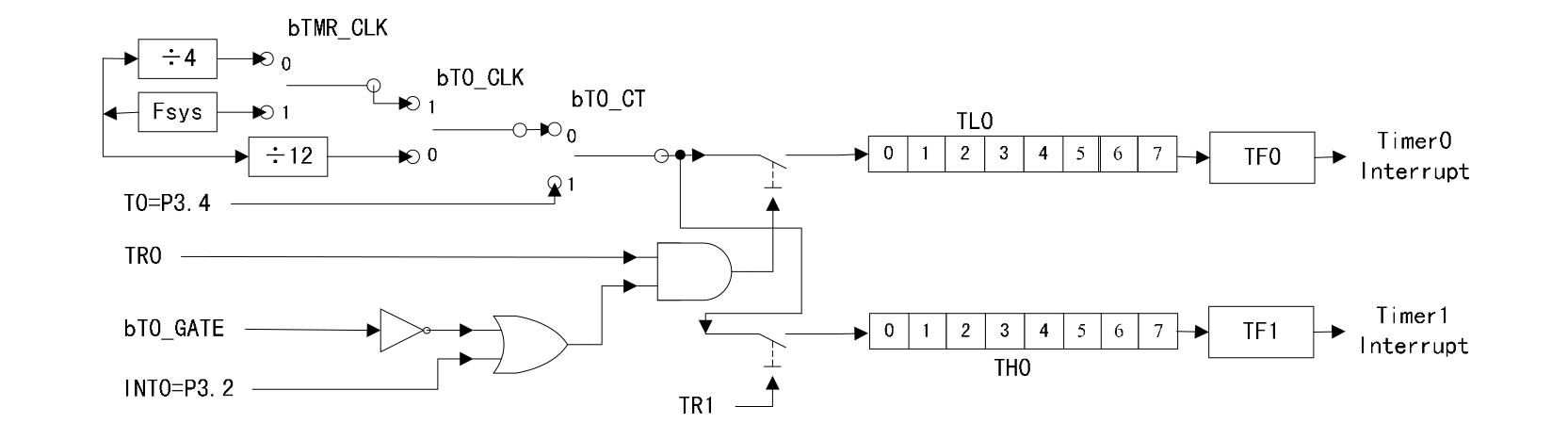

Mode 3: Timer0 is decomposed into two independent 8-bit timers and counters, and the TR1 control bit of Timer1 is borrowed. Timer1 replaces the borrowed TR1 control bit by whether to start mode 3, Timer1 enters mode 3, and Timer1 stops running.

Figure 12.5.1.4 Timer0 Mode 3

12.5.2 Timer2

Timer2 16-bit reload timer/counter mode:

- Set the bits RCLK and TCLK in T2CON to 0, and select the non-serial port baud rate generator mode.

- Set bit C_T2 in T2CON to 0. Select to use the internal clock, go to step (3). Can also set to 1 to select the falling edge of the T2 pin as the count clock, skip step (3).

- Set T2MOD to select the internal clock frequency of the timer. If bT2_CLK is 0, the clock of Timer2 is Fsys / 12. If bT2_CLK is 1, then select Fsys / 4 or Fsys as the clock by T.R_CLK = 0 or 1.

- Set the bit CP_RL2 of T2CON to 0 and select the 16-bit reload timer / counter function of Timer2.

- Set RCAP2L and RCAP2H to the reload value after the timer overflows, set TL2 and TH2 to the initial value of the timer (generally the same as RCAP2L and RCAP2H), set TR2 to 1, and t.rt Timer2.

- The current timer / counter status can be obtained by querying the TF2 or timer 2 interrupts.

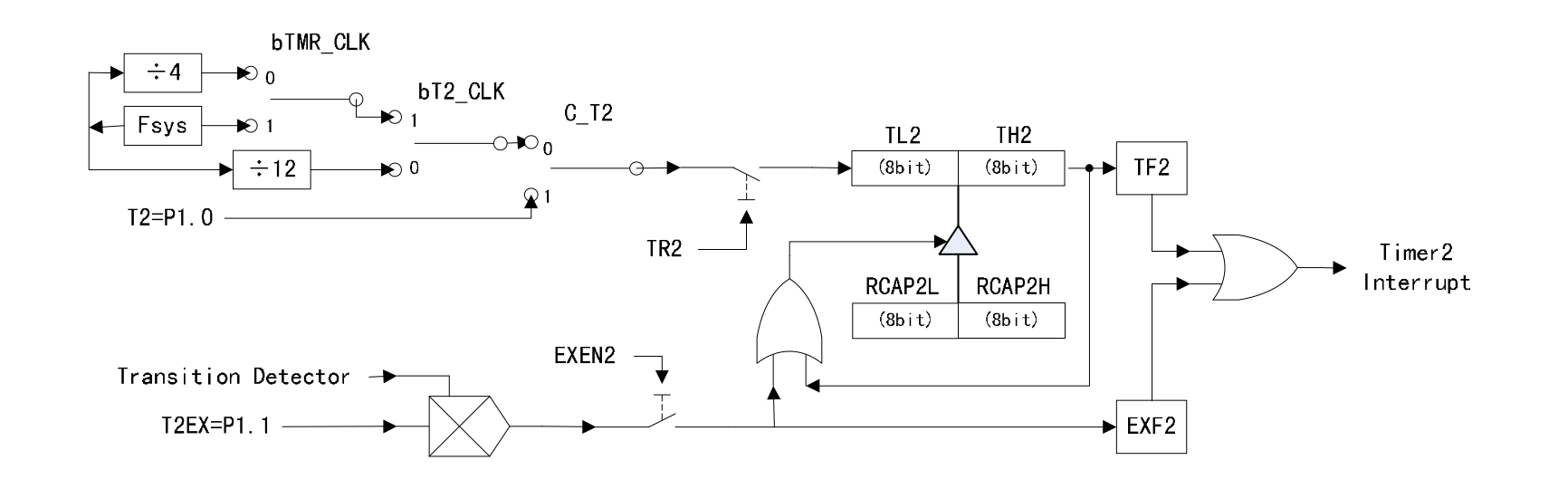

Figure 12.5.2.1 Timer2 16-bit reload timer/counter

Timer2 clock output mode:

Refer to the 16-bit reload timer / counter mode, and then set bit T2OE in T2MOD to 1 to enable the output of the TF2 frequency divided clock from the T2 pin.

Timer2 serial port 0 baud rate generator mode:

- Set bit C_T2 in T2CON to 0 to choose to use the internal clock or set it to 1 to select the falling edge of the T2 pin as the clock. Set the RCLK and TCLK in T2CON to 1 or one of h.m as required. selecting the baud rate generator mode.

- Set T2MOD to select the internal clock frequency of the timer. If bT2_CLK is 0, then the clock of Timer2 is Fsys / 4. If bT2_CLK is 1, then bTMR_CLK = 0 or 1 selects Fsys / 2 or Fsys as the clock. (3) Set RCAP2L and RCAP2H to the reload value after the timer overflows, set TR2 to 1, and start Timer2.

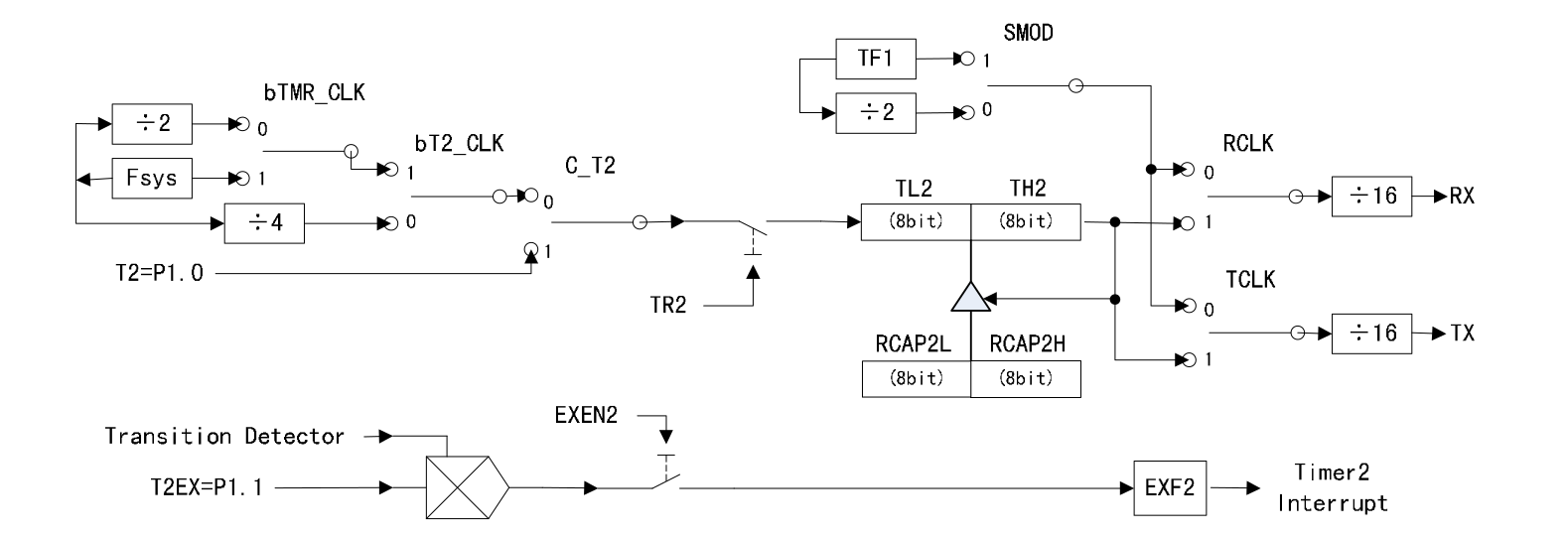

Figure 12.5.2.2 Timer2 UART0 Baud Rate Generator

Timer2 dual channel capture mode:

- Set the bits RCLK and TCLK in T2CON to 0, and select the non-serial port baud rate generator mode.

- Set the bit C_T2 in T2CON to 0. Select to use the internal clock and go to step (3); also set it to select the falling edge of the T2 pin as the count clock and skip step (3).

- Set T2MOD to select the internal clock frequency of the timer. If bT2_CLK is 0, the clock of Timer2 is Fsys/12. If bT2_CLK is 1, then select Fsys/4 or Fsys as the clock by T.R_CLK = 0 or 1.

- Set the bits bT2_CAP_M1 and bT2_CAP_M0 of T2MOD to select the corresponding edge capture mode.

- Set the bit CP_RL2 of T2CON to 1 to select the capture function of T2EX pin by Timer2.

- Set TL2 and TH2 to the initial values of the timer, set TR2 to 1, and start Timer2.

- When the CAP2 capture is completed, RCAP2L and RCAP2H will save the current TL2 and TH2 count values and set EXF2 to generate an interrupt.The next captured RCAP2L and RCAP2H i.l be between the last captured RCAP2L and RCAP2H The difference is the signal width between the two valid edges.

- If bit C_T2 in T2CON is 0 and bit bT2_CAP1_EN in T2MOD is 1, then the capture function of Timer2 on the T2 pin will be enabled at the same time. When CAP1 capture is completed, T2CAP1L and T2CAP1H will save the current TL2 and TH2 And the CAP1F bit is set to generate an interrupt.

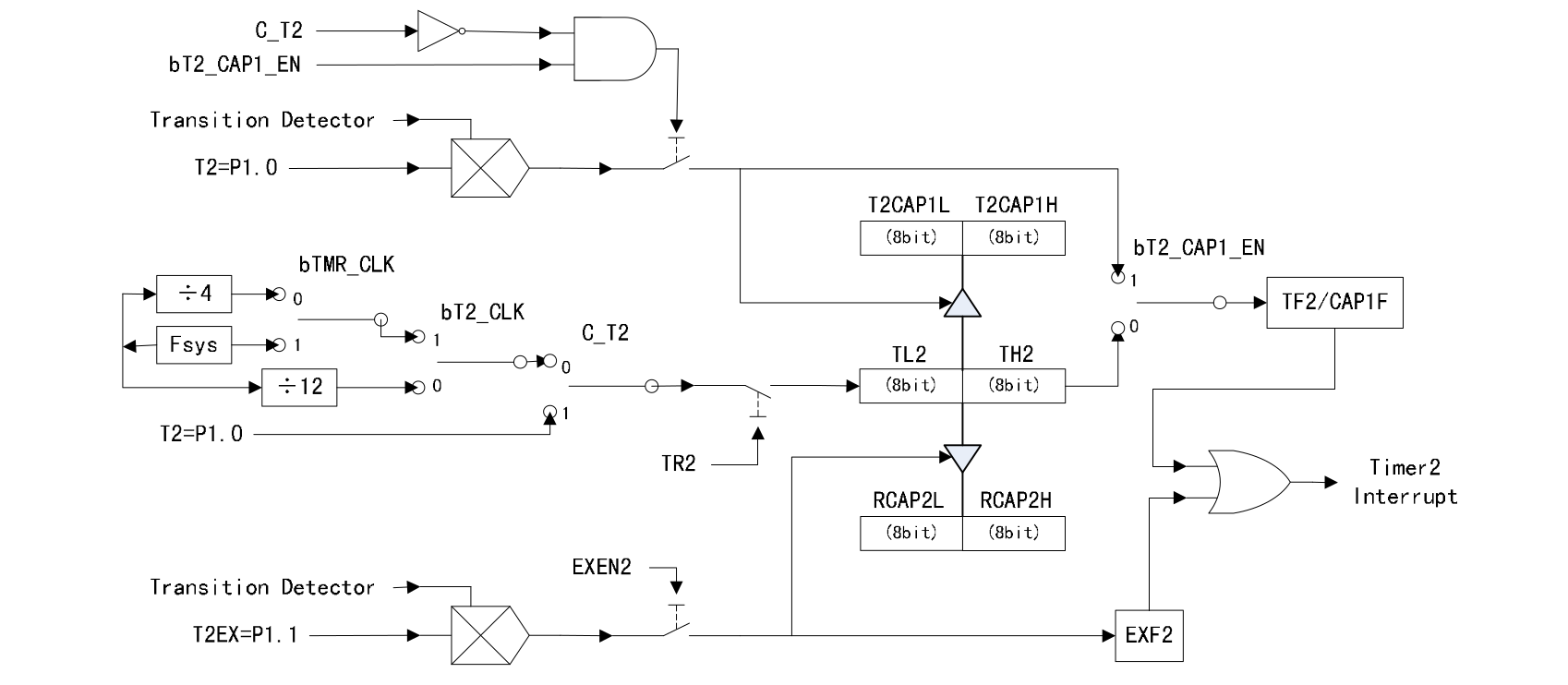

Figure 12.5.2.3 Timer2 capture mode

12.5.3 Timer3

- Set the bit bT3_EN_CK_SE in T3_SETUP to 1, enable the Timer3 clock division setting register T3_CK_SE, set the division factor, and count the clock to Fsys / T3_CK_SE. Clear T._EN_CK_SE after the setting is completed.

- Set the T3_END counting end value or the total number of PWM cycles.

- Turn on interrupt enable in T3_SETUP as required.

- Set each control bit in T3_CTRL, select the mode, and clear bT3_CLR_ALL, set bT3_CNT_EN to start Timer3.

- Set T3_DMA_AL and T3_DMA_AH and T3_DMA_CN as required, set bT3_DMA_EN to enable the DMA function.

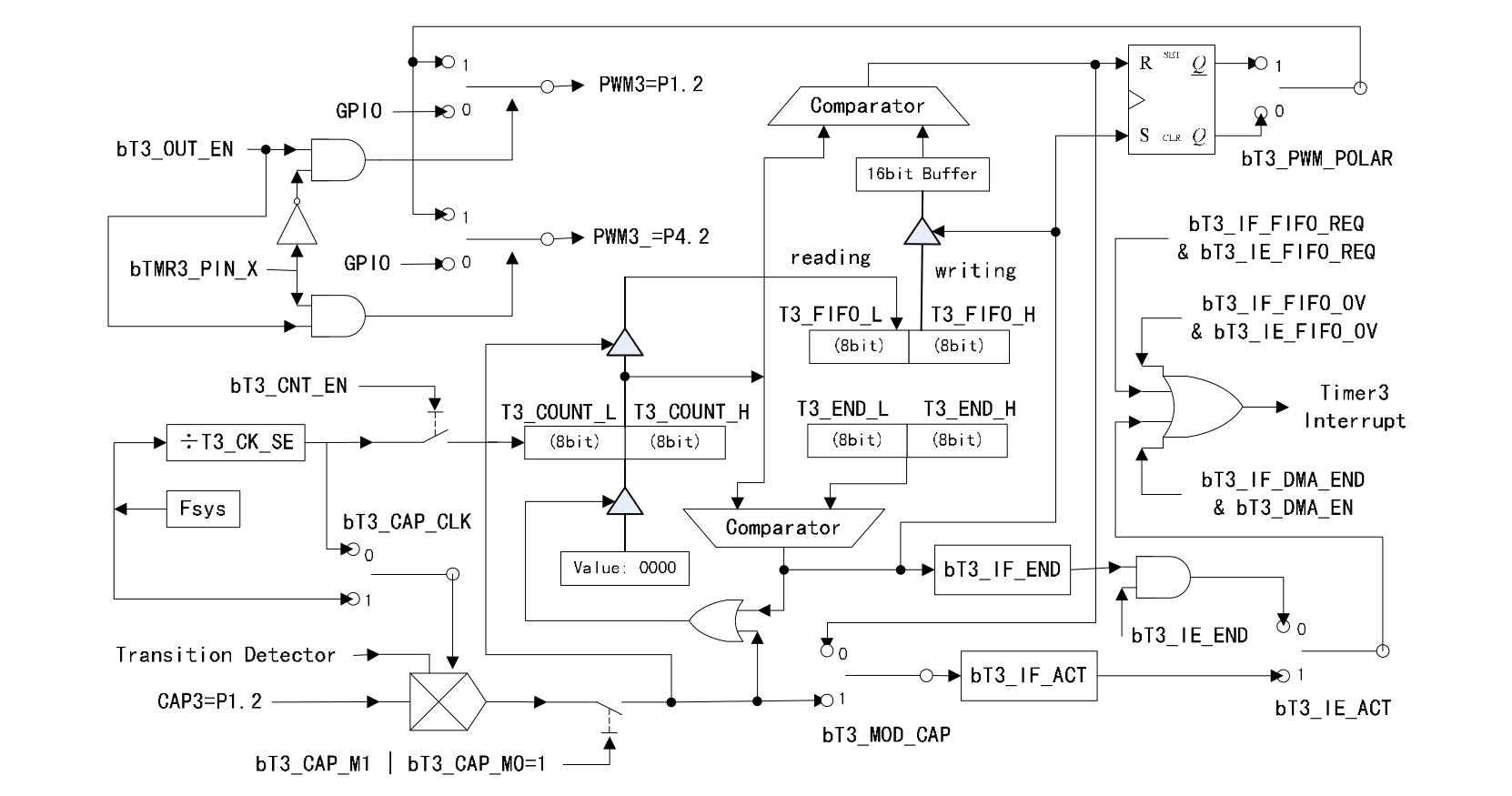

Figure 12.5.3.1 Timer3 16-bit timer/PWM/capture

Data format captured by Timer3:

Timer3 can be used to capture the width between two valid edges of the signal.The width is expressed by the divided clock count. During or after the capture, the width data can be obtained through DMA or directly reading the FIFO.The data is 16 bits. The most significant bit is the identification bit and the lower 15 bits are the width count. After signal capture is enabled, data will be generated every time a valid edge is detected or every timer overflows.Because the data generated at the first valid edge is the width from the time when signal capture is enabled, not two valid edges Width, so the first data captured is usually discarded.

(1). bT3_CAP_M1 and bT3_CAP_M0 = 11

The rising edge is valid, capturing the signal width from the rising edge to the rising edge, that is, the rising edge is activated. If the highest bit of the data is 1, it means that the signal width has overflowed the counting end value, that is, if the timing exceeds T3_END and the next rising edge has not been found, the width value must be added to the width of the next data whose highest bit is 0. The most significant bit is 0, which means that the width is the width between the end of a certain rising edge, and whether the lower 15 bits are accumulated forward according to whether the most significant bit of some previous data is 1. In this mode, it is recommended to set T3_END to detect ultra-wide signals or end signals for special purposes, and normal signals should not overflow.

For example, T3_END is set to 4000h, and the raw data sequence collected is as follows

1234h, 2345h, 0456h, C000h, C000h, 1035h, 3579h, C000h, 2468h, and 0987h are combined to obtain the interval between each rising edge: 1234h, 2345h, 0456h, 9035h, 3579h, 6468h, 0987h

(2). bT3_CAP_M1 and bT3_CAP_M0 = 10

Same as above, but the falling edge is valid, capturing the signal width from the rising edge to the falling edge, that is, the falling edge is activated.

(3). bT3_CAP_M1 and bT3_CAP_M0 = 01

Any edge is valid, capturing the signal width from any edge to any edge, that is, the level change is activated. If the highest bit of the data is 1, then the width is a high-level width, that is, from the rising edge to the falling edge. If the highest bit of the data is 0, then the width is a low-level width, that is, from the falling edge to the rising edge. The lower 15 bits after masking the most significant bits are width values counted by the divided clock. In this mode, it is recommended to set T3_END to a larger value to avoid timing overflow, but it must not exceed 15 digits of valid data.