14. Synchronous Serial Interface SPI

14.1 Introduction to SPI

CH559 chip provides 2 SPI interfaces for high-speed synchronous data transmission with peripherals.

SPI0 features:

- Support master mode and slave mode.

- Support mode 0 and mode 3 clock mode.

- Optional 3-wire full duplex or 2-wire half duplex mode.

- Optional MSB high bit is transmitted first or LSB low bit is transmitted first.

- The clock frequency is adjustable, up to half of the system main frequency.

- Built-in 3-byte receive FIFO and 1-byte transmit FIFO.

- Support multiple interrupts.

SPI1 features:

- Only support master mode, MSB high bit is sent first.

- Support mode 0 and mode 3 clock mode.

- Optional 3-wire full duplex or 2-wire half duplex mode.

- The clock frequency is adjustable, up to half of the system main frequency.

14.2 SPI Register

Table 14.2.1 List of SPI Related Registers

| Name | Address | Description | Reset value |

|---|---|---|---|

| SPI0_SETUP | FCh | SPI0 setup register | 00h |

| SPI0_S_PRE | FBh | SPI0 Slave Mode Preset Data Register | 20h |

| SPI0_CK_SE | FBh | SPI0 Clock Divider Setting Register | 20h |

| SPI0_CTRL | FAh | SPI0 Control Register | 02h |

| SPI0_DATA | F9h | SPI0 data transmit / receive register | xxh |

| SPI0_STAT | F8h | SPI0 status register | 08h |

| SPI1_CK_SE | B7h | SPI1 clock divider setting register | 20h |

| SPI1_CTRL | B6h | SPI1 control register | 02h |

| SPI1_DATA | B5h | SPI1 data transmission and reception register | xxh |

| SPI1_STAT | B4h | SPI1 status register | 08h |

14.2.1 SPI0 Related Registers

SPI0 setup register (SPI0_SETUP):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bS0_MODE_SLV | RW | SPI0 master-slave mode selection bit, if this bit is 0, SPI0 is master mode. If this bit is 1, SPI0 is slave mode / device mode | 0 |

| 6 | bS0_IE_FIFO_OV | RW | FIFO overflow interrupt enable bit in slave mode, this bit is 1 to enable FIFO overflow interrupt. If this bit is 0, FIFO overflow does not generate interrupt | 0 |

| 5 | bS0_IE_FIRST | RW | Receive the first byte to complete the interrupt enable bit in slave mode. When this bit is 1, the interrupt is triggered when the first data byte is received in slave mode. When the bit is 0, no interrupt is generated when the first byte is received. | 0 |

| 4 | bS0_IE_BYTE | RW | Data byte transfer completion interrupt enable bit, this bit is 1 to enable byte transfer completion interrupt. When this bit is 0, byte transfer completion does not generate an interrupt | 0 |

| 3 | bS0_BIT_ORDER | RW | Bit order control bit of the data byte. If this bit is 0, the MSB high-order bit comes first. If this bit is 1, the LSB low-order bit comes first. | 0 |

| 2 | reserved | R0 | reserved | 0 |

| 1 | bS0_SLV_SELT | R0 | Chip select active status bit in slave mode, this bit is 0 if it is not currently selected. This bit is 1 if it is currently selected | 0 |

| 0 | bS0_SLV_PRELOAD | R0 | Preload data status bit in slave mode, this bit is 1 to indicate that it is currently in the preload status after the chip select is valid but before the data has been transferred | 0 |

SPI0 clock divider setting register (SPI0_CK_SE):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | SPI0_CK_SE | RW | Setting the SPI0 Clock Divider in Master Mode | 20h |

SPI0 Slave Mode Preset Data Register (SPI0_S_PRE):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | SPI0_S_PRE | RW | Preload the first transfer data in slave mode | 20h |

SPI0 control register (SPI0_CTRL):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | bS0_MISO_OE | RW | MISO output enable control bit for SPI0, this bit is 1 to enable output. This bit is 0 to disable output | 0 |

| 6 | bS0_MOSI_OE | RW | SPI0 MOSI output enable control bit, this bit is 1 to enable output. This bit is 0 to disable output | 0 |

| 5 | bS0_SCK_OE | RW | SCK output enable control bit for SPI0, this bit is 1 to enable output. This bit is 0 to disable output | 0 |

| 4 | bS0_DATA_DIR | RW | SPI0 data direction control bit. This bit is 0 to output data. Only write FIFO is used as a valid operation to start an SPI transmission. This bit is 1 to input data and write or read FIFO are both a valid operation to start a SPI transmission | 0 |

| 3 | bS0_MST_CLK | RW | SPI0 Master clock mode control bit, this bit is 0 for mode 0, the default low level when SCK is idle. 1 for mode 3, SCK default high level | 0 |

| 2 | bS0_2_WIRE | RW | SPI0 2-wire half-duplex mode enable bit. If this bit is 0, 3-wire full-duplex mode, including SCK, MOSI, and MISO. This bit is 1 2-wire half-duplex mode, including SCK, MISO. | 0 |

| 1 | bS0_CLR_ALL | RW | This bit is 1 to clear the SPI0 interrupt flag and FIFO, which needs to be cleared by software | 1 |

| 0 | bS0_AUTO_IF | RW | Enable bit for automatically clearing the byte reception completion interrupt flag through a valid FIFO operation. When this bit is 1, the byte reception completion interrupt flag S0_IF_BYTE is automatically cleared during a valid FIFO read and write operation. | 0 |

SPI0 data transmit and receive register (SPI0_DATA):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | SPI0_DATA | RW | Including sending and receiving two physically separate FIFOs, read operations correspond to receive data FIFOs, write operations correspond to send data FIFOs, and valid read and write operations can initiate an SPI transmission | xxh |

SPI0 status register (SPI0_STAT):

| Bit | Name | Access | Description | Reset value | |

|---|---|---|---|---|---|

| 7 | S0_FST_ACT | R0 | This bit is 1 to indicate that the current status is completed when the first byte is received in slave mode | 0 | |

| 6 | S0_IF_OV | RW | FIFO overflow flag in slave mode. A 1 in this bit indicates a FIFO overflow interrupt. A 0 in this bit indicates no interrupt. Clear by direct bit access or write 1 to clear. When bS0_DATA_DIR = 0, the interrupt is triggered by the sending FIFO empty. When bS0_DATA_DIR = 1, the interrupt is triggered by the receiving FIFO full. | 0 | |

| 5 | S0_IF_FIRST | RW | Receives the first byte completion interrupt flag bit in slave mode. A 1 in this bit indicates that the first byte was received. Clear by direct bit access or write 1 Clear | 0 | |

| 4 | S0_IF_BYTE | RW | Data byte transfer complete interrupt flag. When this bit is 1, it indicates that one byte transfer is completed. Direct bit access Clear or write 1 clear, or clear by FIFO valid operation when bS0_AUTO_IF = 1 | 0 | |

| 3 | S0_FREE | R0 | SPI0 idle flag bit, this bit is 1 means there is no SPI shift at present, usually in the gap period between data bytes | 1 | |

| 2 | S0_T_FIFO | R0 | SPI0 transmit FIFO count, valid value is 0 or 1 | 0 | |

| 1 | S0_R_FIFO1 | R0 | SPI0 receive FIFO count bit 1 | Valid values are 0 or 1 or 2 or 3 | 0 |

| 0 | S0_R_FIFO0 | R0 | SPI0 receive FIFO count bit 0 | 0 | |

14.2.2 SPI1 Register Description

SPI1 status register (SPI1_STAT):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:5] | reserved | RO | reserved | 000b |

| 4 | bS1_IF_BYTE | RO | Data byte transfer completed interrupt flag bit. When this bit is 1, it indicates that a byte transfer is completed. Direct bit access Cleared or written 1 cleared, or cleared by valid FIFO operation when bS1_AUTO_IF = 1 | 0 |

| 3 | bS1_FREE | RW | SPI1 idle flag bit, this bit is 1 means there is no SPI shift at present, usually in the gap period between data bytes | 1 |

| [2:0] | reserved | RO | reserved | 000b |

SPI1 data transmit and receive register (SPI1_DATA):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | SPI1_DATA | RW | It is actually an SPI data shift register. Read is used to receive data and write is used to send data. Effective read and write operations can start an SPI transfer. | xxh |

SPI1 control register (SPI1_CTRL):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 |

| 7 | bS1_MISO_OE | RW | MISO1 output enable control bit for SPI1, this bit is 1 to enable output. This bit is 0 to disable output | 0 |

| 6 | Reserved | RO | reserved | 0 |

| 5 | bS1_SCK_OE | RW | SCK1 output enable control bit for SPI1, this bit is 1 to enable SCK1 output, if bS1_2_WIRE = 0, then MOSI1 output enable will be enabled at the same time. This bit is 0 to disable output | 0 |

| 4 | bS1_DATA_DIR | RW | SPI1 data direction control bit. This bit is 0 to output data. Only write SPI1_DATA as a valid operation to start an SPI transmission. This bit is 1 to input data. Writing or reading SPI1_DATA is a valid operation to start a SPI. transmission | 0 |

| 3 | bS1_MST_CLK | RW | SPI1 clock mode control bit, this bit is 0 for mode 0, SCK1 defaults to low level when idle. This bit is 1 for mode 3, SCK1 defaults to high level | 0 |

| 2 | bS1_2_WIRE | RW | SPI1 2-wire half-duplex mode enable bit, this bit is 0, then 3-wire full duplex mode, including SCK1, MOSI1, MISO1. This bit is 1, then 2-wire half-duplex mode, including SCK1, MISO1 | 0 |

| 1 | bS1_CLR_ALL | RW | This bit is 1 to clear the SPI1 interrupt flag and FIFO, which needs to be cleared by software | 1 |

| 0 | bS1_AUTO_IF | RW | Enable bit for automatically clearing the byte reception completion interrupt flag through the SPI1_DATA valid operation. When this bit is 1, it automatically clears the byte reception completion interrupt flag bS1_IF_BYTE when the SPI1_DATA is valid | 0 |

SPI1 clock divider setting register (SPI1_CK_SE):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | SPI1_CK_SE | RW | Set the SPI1 clock division factor | 20h |

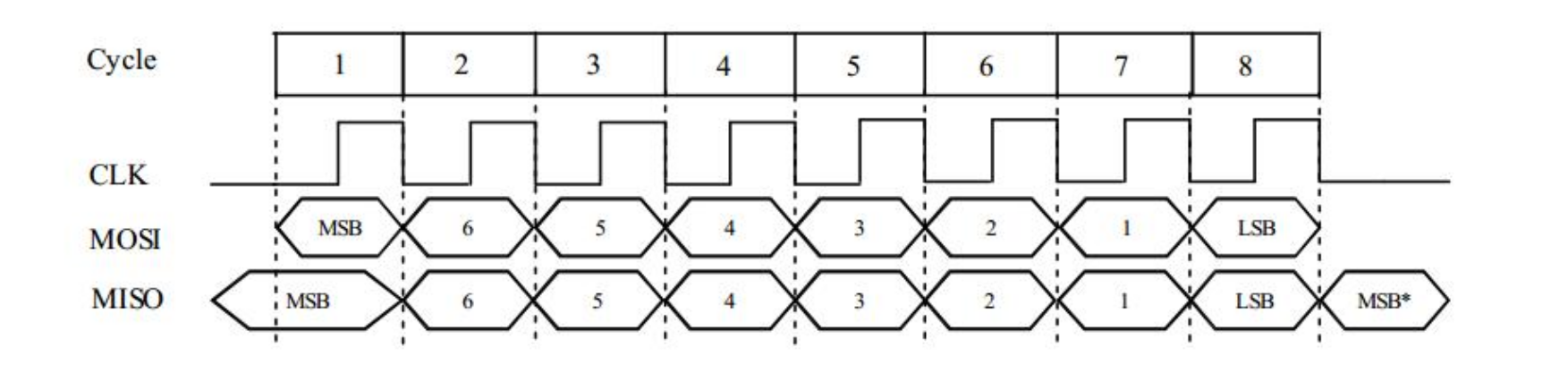

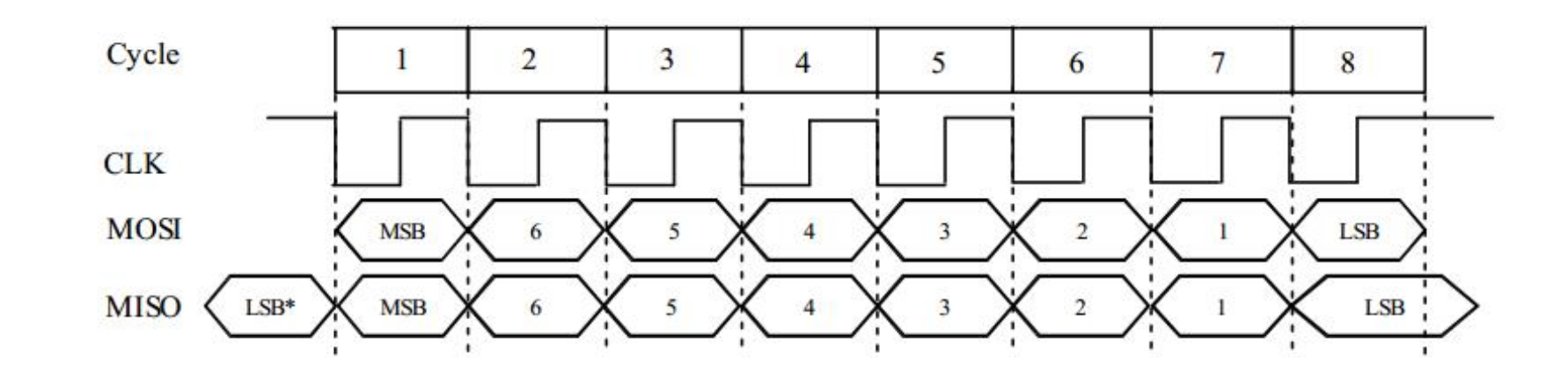

14.3 SPI Transmission Format

The SPI master mode supports two transmission modes, Mode 0 and Mode 3. You can select by setting bit bSn_MST_CLK in the SPI control register SPIn_CTRL. CH559 always samples MISO data on the rising edge of CLK. The data transmission format is shown in the figure below.

Mode 0: bSn_MST_CLK = 0

Figure 14.3.1 SPI Mode 0 Timing Diagram

Mode 3: bSn_MST_CLK = 1

Figure 14.3.2 SPI Mode 3 Timing Diagram

14.4 SPI Configuration

14.4.1 SPI Master Mode Configuration

In SPI master mode, the SCK pin outputs a serial clock, and the chip select output pin can be designated as any I/O pin.

SPI0 configuration steps:

- Set the SPI clock frequency division setting register SPI0_CK_SE to configure the SPI clock frequency.

- Set bit bS0_MODE_SLV of the SPI setting register SPI0_SETUP to 0, and configure it as the master mode.

- Set the bit bS0_MST_CLK of the SPI control register SPI0_CTRL and set it to mode 0 or 3 as required.

- Set the bS0_SCK_OE and bS0_MOSI_OE bits of the SPI control register SPI0_CTRL to 1, and set the bS0_MISO_OE bit to 0, set the direction of P1 port bSCK, bMOSI as the output, bMISO as the input, and the chip select pin as the output.

Data sending process:

- Write the SPI0_DATA register, write the data to be sent to the FIFO, and automatically start an SPI transfer.

- Wait for S0_FREE to be 1, indicating that the transmission is complete, and can continue to send the next byte.

Data receiving process:

- Write the SPI0_DATA register and write any data such as 0FFh to the FIFO to start an SPI transfer.

- Wait for S0_FREE to be 1, indicating that the reception is complete. You can read SPI0_DATA to get the received data.

- If the previous bS0_DATA_DIR is set to 1, the above read operation will also start the next SPI transmission, otherwise it will not start.

14.4.2 SPI Slave Mode Configuration

Only SPI0 supports slave mode. In slave mode, the SCK pin is used to receive the serial clock of the connected SPI master.

- Set bit bS0_MODE_SLV of SPI0 setting register SPI0_SETUP to 1, and configure it as slave mode.

- Set the bits bS0_SCK_OE and bS0_MOSI_OE of the SPI0 control register SPI0_CTRL to 0, set bS0_MISO_OE to 1, set the direction of P1 port bSCK, bMOSI and bMISO, and chip select pins as inputs. When the SCS chip select is active (low level), MISO will automatically enable the output. At the same time, it is recommended to set the MISO pin to high-impedance input mode (bP1_OC = 0, P1_DIR [6] = 0, P1_PU [6] = 0), so that MISO does not output during chip select invalidation, which facilitates sharing the SPI bus.

- Optional, set the SPI slave mode preset data register SPI0_S_PRE, which is used to automatically load into the buffer for external output after being selected by the chip for the first time. After 8 serial clocks, that is, the first data byte transfer is completed, CH559 gets the first byte data (possibly a command code) from the external SPI host, and the external SPI host exchanges the preset data in SPI0_S_PRE (possibly Is a status value). Bit 7 of the register SPI0_S_PRE will be automatically loaded on the MISO pin during the low period of SCK after the SPI chip select is active. For SPI mode 0, if CH559 is preset with bit 7 of SPI0_S_PRE, then the external SPI host will select the SPI chip select When the data is valid but not yet transmitted, the preset value of bit 7 of SPI0_S_PRE can be obtained by querying the MISO pin, so that the value of bit 7 of SPI0_S_PRE can be obtained only by validating the SPI chip select.

Data sending process:

Query S0_IF_BYTE or wait for an interrupt. After each SPI data byte transfer is completed, write to the SPI0_DATA register and write the data to be sent to the FIFO. Or wait for S0_FREE to change from 0 to 1 to continue sending the next byte.

Data receiving process:

Query S0_IF_BYTE or wait for an interrupt. After each SPI data byte transfer is completed, read the SPI0_DATA register to get the received data from the FIFO. Query MASK_S0_RFIFO_CNT (that is, S0_R_FIFO1 and S0_R_FIFO0) to get the number of bytes remaining in the FIFO.