6. Memory structure

6.1 Memory space

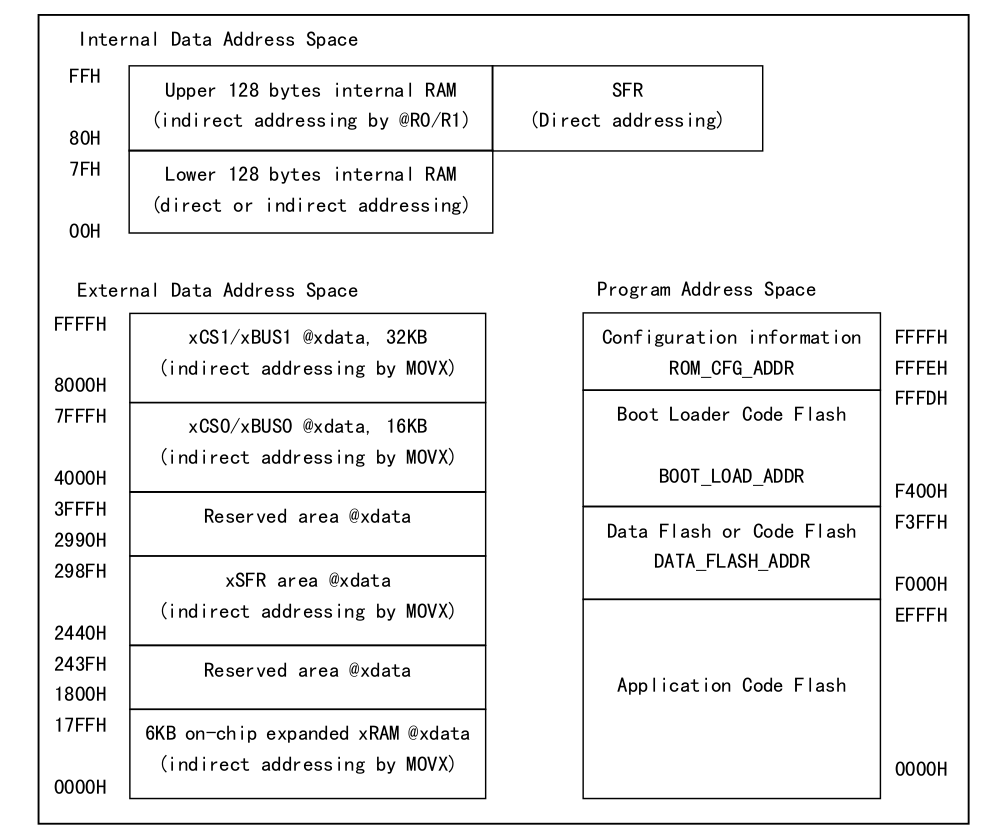

CH559 addressing space is divided into program storage space, internal data storage space, and external data storage space.

Figure 6.1 Memory Structure

6.2 Program Storage Space

The program memory space is 64KB. As shown in Figure 6.1, it is all used for flash-ROM, including Code Flash area for saving instruction code, Data Flash area for saving non-volatile data, and Configuration Information area for configuration information.

The Data Flash address range is F000h to F3FFH. It supports single-byte read (8-bit), double-byte write (16-bit), and block erase (1K byte) operations. The data remains unchanged after the chip is powered off. Make Code Flash.

Code Flash includes application code for low address areas and bootstrap code for high address areas. You can also combine these two areas and Data Flash to hold a single application code.

Configuration Information Configuration Information A total of 16 bits of data, set by the programmer as needed, refer to Table 6.1.

Table 6.2 Description of flash-ROM configuration information

| Bit | Name | Description | Reset value |

|---|---|---|---|

| 15 | Code_Protect | Code and data protection mode in flash-ROM: 0-Prohibit the programmer to read, the program is confidential; 1-Allow readout | 0/1 |

| 14 | No_Boot_Load | Enable BootLoader boot code startup mode: 0-started from the 0000h address application. 1-start from the bootloader of the F400h address | 1 |

| 13 | En_Long_Reset | Enable additional delay reset during power-on reset: 0-standard short reset; 1-wide reset, additional 87mS reset time | 0 |

| 12 | XT_OSC_Strong | Select the external drive capability of the crystal oscillator: 0-standard; 1-enhanced | 0 |

| 11 | En_P5.7_RESET | Enable P5.7 as a manual reset input pin: 0-disable; 1-enable RST | 1 |

| 10 | En_P0_Pullup | Enable internal pull-up resistor for port P0 during system reset: 0-Pull-up resistor disabled after reset. 1-Pull-up resistor enabled after reset | 1 |

| 9 | Must_1 | (Automatically set to 1 by the programmer as needed) | 1 |

| 8 | Must_0 | (automatically set to 0 by the programmer as needed) | 0 |

| [7:0] | All_1 | (Automatically set to FFh by the programmer as needed) | FFh |

6.3 Data Storage Space

The internal data storage space is 256 bytes in total. As shown in Figure 6.1, it is used for SFR and iRAM. iRAM is used for stack and fast data temporary storage. It can be subdivided into working registers R0-R7, bit variables bdata, bytes. Variable data, idata, etc.

The external data storage space is 64KB in total, as shown in Figure 6.1, and partially used for 6KB on-chip expansion of xRAM and xSFR. Except for the two reserved areas, the remaining 4000h to FFFFh address range is the external bus area.

6.4 flash-ROM register

Table 6.4 List of flash-ROM operation registers

| Name | Address | Description | Reset value |

|---|---|---|---|

| ROM_DATA_H | 8Fh | flash-ROM data register high byte | xxh |

| ROM_DATA_L | 8Eh | flash-ROM data register low byte | xxh |

| ROM_DATA | 8Eh | ROM_DATA_L and ROM_DATA_H form a 16-bit SFR | xxxxh |

| ROM_STATUS | 86h | flash-ROM status register (read only) | 80h |

| ROM_CTRL | 86h | flash-ROM control register (write only) | 00h |

| ROM_ADDR_H | 85h | flash-ROM address register high byte | xxh |

| ROM_ADDR_L | 84h | flash-ROM address register low byte | xxh |

| ROM_ADDR | 84h | ROM_ADDR_L and ROM_ADDR_H form a 16-bit SFR | xxxxh |

flash-ROM address register (ROM_ADDR):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | ROM_ADDR_H | RW | Flash-ROM address high byte | xxh |

| [7:0] | ROM_ADDR_L | RW | Flash-ROM address low byte, only supports even address | xxh |

flash-ROM data register (ROM_DATA):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | ROM_DATA_H | RW | flash-ROM data to be written high byte | xxh |

| [7:0] | ROM_DATA_L | RW | flash-ROM data to be written low byte | xxh |

flash-ROM control register (ROM_CTRL):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| [7:0] | ROM_CTRL | W0 | flash-ROM control register | 00h |

flash-ROM status register (ROM_STATUS):

| Bit | Name | Access | Description | Reset value |

|---|---|---|---|---|

| 7 | Reserved | R0 | Reserved | 1 |

| 6 | bROM_ADDR_OK | R0 | flash-ROM operation address valid status bit: If the bit is 0, the parameter is invalid; 1 means the address is valid. | 0 |

| [5:2] | Reserved | R0 | Reserved | 0000b |

| 1 | bROM_CMD_ERR | R0 | flash-ROM operation command error status bit: A bit of 0 indicates that the command is valid. A value of 1 indicates an unknown command. | 0 |

| 0 | bROM_CMD_TOUT | R0 | flash-ROM operation result status bit: A bit of 0 indicates that the operation was successful. A value of 1 indicates that the operation timed out. | 0 |

6.5 flash-ROM operation steps

Erase the flash-ROM and change all the data bits in the target block to 1:

- enable the security mode, SAFE_MOD = 55h; SAFE_MOD = 0AAh;

- set the global configuration register GLOBAL_CFG to enable write enable (bCODE_WE or bDATA_WE corresponds to code or data);

- set the address register ROM_ADDR, write 16-bit target address, the actual only high 6 bits are valid;

- Set the operation control register ROM_CTRL to 0A6h to perform the block erase operation, and the program will automatically pause during the operation;

- After the operation is completed, the program resumes operation. At this time, the status register ROM_STATUS can be queried to check the operation status; if multiple blocks are to be erased, the steps (3), (4), and (5) are repeated;

- enter safe mode again, SAFE_MOD = 55h; SAFE_MOD = 0AAh;

- Set the global configuration register GLOBAL_CFG to enable write protection (bCODE_WE=0, bDATA_WE=0).

Write flash-ROM to change part of the data bits in the target double byte from 1 to 0:

- enable the security mode, SAFE_MOD = 55h; SAFE_MOD = 0AAh;

- set the global configuration register GLOBAL_CFG to enable write enable (bCODE_WE or bDATA_WE corresponds to code or data);

- set the address register ROM_ADDR, write 16-bit target address, the actual only 15 high;

- set the data register ROM_DATA, write 16 bits of data to be written, steps (3), (4) can be reversed;

- Set the operation control register ROM_CTRL to 09Ah to perform the write operation, and the program will automatically suspend the operation during the operation;

- After the operation is completed, the program resumes operation. At this time, the status register ROM_STATUS can be queried to check the operation status; if multiple data is to be written, the steps (3), (4), (5), and (6) are repeated;

- enter safe mode again, SAFE_MOD = 55h; SAFE_MOD = 0AAh;

- Set the global configuration register GLOBAL_CFG to enable write protection (bCODE_WE=0, bDATA_WE=0).

read flash-ROM:

- Read the code or data of the target address directly using the MOVC instruction or by a pointer to the program memory space.

6.6 On-board programming and ISP downloads

When the configuration information Code_Protect=1, the code and data in the CH559 chip flash-ROM can be read and written by the external programmer through the synchronous serial interface; when the configuration information Code_Protect=0, the code and data in the flash-ROM are protected. Can not be read, but can be erased, and re-powered after erasing to release code protection.

When the CH559 chip is pre-installed with the BootLoader bootloader, the CH559 can support multiple ISP download methods such as USB or asynchronous serial port to load the application; but without the bootloader, the CH559 can only be written to the bootloader by an external dedicated programmer. Or an application. In order to support on-board programming, five connection pins between CH559 and the programmer need to be reserved in the circuit.

Table 6.6.1 Connection Pins to the Programmer

| Pin | GPIO | Pin description |

|---|---|---|

| RST | P5.7 | Reset control pin in programming state, high level allows entry into programming state |

| SCS | P1.4 | Chip select input pin in programming state, default high level, active low |

| SCK | P1.7 | Clock input pin in programming state |

| MOSI | P1.5 | Data input pin in programming state |

| MISO | P1.6 | Data output pin in programming state |

6.7 chip unique ID number

Each microcontroller is shipped with a unique ID number, the chip identification number. The ID data and its checksum are 8 bytes in total, and are stored in the area where the offset address of the dedicated read-only memory is 20h. It can be obtained by reading Code Flash similarly during the period when E_DIS is 1 to close the global interrupt. Please refer to the C language example program GETID.C for operation.

Table 6.7.1 Chip ID Address Table

| Offset address | ID data description |

|---|---|

| 20h, 21h | ID first word data, followed by the lowest byte and the next lowest byte of the ID number |

| 22h, 23h | ID second word data, followed by the next highest byte of the ID number, high byte |

| 24h, 25h | ID last word data, followed by the next highest byte and highest byte of the 48-bit ID number |

| 26h, 27h | 16-bit cumulative sum of ID first word, second word, last word data, used for ID verification |

The ID number can be used with the download tool to encrypt the target program. For general applications, just use the first 32 digits of the ID number.